Hi Readers,

Attended 4th Edition of DVCON-17 India on Sep 14th & 15th in Bangalore.Summarizing the key highlights below.

DVCON India got an outstanding response with houseful gathering of DV Engineers, It started with keynote speeches followed by Tutorials and Panel Discussions on current topics like Machine Learning, Emulation,PSS, etc.The day ended with a Gala Dinner and created an opportunity to meet peers from other companies.

Day 2 stared with a keynote speech on "Driving the Next Big Wave in Verification by Ravi Subramanian from Mentor Graphics followed by paper and poster sessions.

There were handful papers on UVM, attended below papers in the UVM Track.

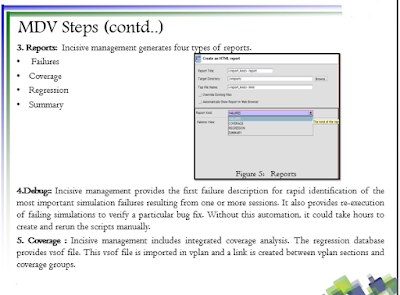

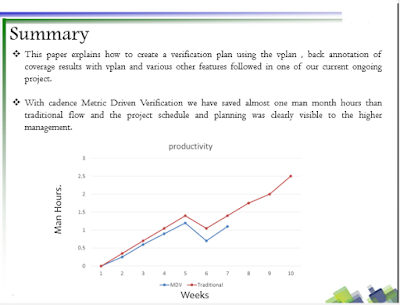

I have presented 2 papers as mentioned below.

1. Trials and Tribulations of migrating a native UVM Testbench from Simulation to Emulation

Conference provided networking opportunities , met some old friends and made new friends as well, also learnt new technologies. Meet you again in DVCON-18.

Happy Reading..!

Thanks,

Vikas Billa

Attended 4th Edition of DVCON-17 India on Sep 14th & 15th in Bangalore.Summarizing the key highlights below.

DVCON India got an outstanding response with houseful gathering of DV Engineers, It started with keynote speeches followed by Tutorials and Panel Discussions on current topics like Machine Learning, Emulation,PSS, etc.The day ended with a Gala Dinner and created an opportunity to meet peers from other companies.

Day 2 stared with a keynote speech on "Driving the Next Big Wave in Verification by Ravi Subramanian from Mentor Graphics followed by paper and poster sessions.

There were handful papers on UVM, attended below papers in the UVM Track.

- How to inject errors in UVM RAL: Explained by using callbacks

- Adopting UVM for FPGA & RTL Engineers: Explained about go2uvm app

- Real world clock generator: Explained on how to develop a clock agent with all possible options like jitter etc…

- Embedded UVM: Explained how to use it on raspberry pi

- The coverage generator: script to automate functional coverage coding

I have presented 2 papers as mentioned below.

1. Trials and Tribulations of migrating a native UVM Testbench from Simulation to Emulation

2. A 360 view of UVM Events

Got good response from the audience, The full paper can be found in DVCON-17 archives shortly.

Link: https://dvcon-india.org/

Link: https://dvcon-india.org/

Happy Reading..!

Thanks,

Vikas Billa