Please find the posters from the below link.

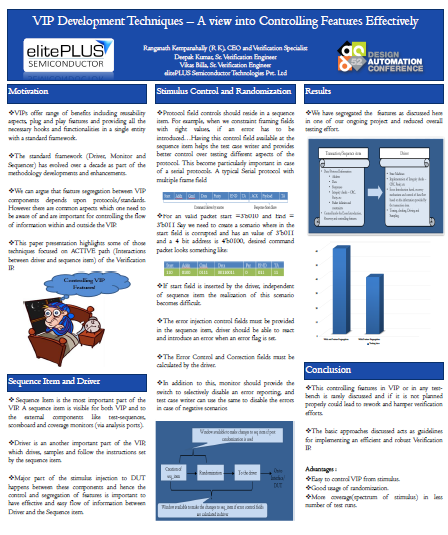

Paper Title: VIP Development Techniques – A view into Controlling Features Effectively

Link: VIP_Development_Techniques.pdf

Abstract: VIPs offer range of benefits including reusability aspects, plug and play features and providing all the necessary hooks and functionalities in a single entity with a standard framework.

The standard framework (Driver, Monitor and Sequencer) has evolved over a decade as part of the methodology developments and enhancements.

We can argue that feature segregation between VIP components depends upon protocols/standards. However there are common aspects which one need to be aware of and are important for controlling the flow of information within and outside the VIP.

This paper presentation highlights some of those techniques focused on ACTIVE path (Interactions between driver and sequence item) of the Verification IP.

Paper Title: Developing Common UVM Testbench for Simulation and Emulation Platforms to

Reduce Verification Effort Across Different Abstraction Levels

Link: Abstarction_Levels.pdf

Abstract: Today’s traditional verification flow involves verification at multiple levels of abstraction. So the testbench also needs to be adjusted/modified at different abstractions from transaction-level simulation, RTL simulation to hardware acceleration.

An ideal solution is to make use of an advanced, automated verification environment across different abstraction levels, which helps in enhancing the overall performance gain, productivity and faster verification closure.

Thanks for reading, please inbox me for any queries/suggestions

Paper Title: VIP Development Techniques – A view into Controlling Features Effectively

Link: VIP_Development_Techniques.pdf

Abstract: VIPs offer range of benefits including reusability aspects, plug and play features and providing all the necessary hooks and functionalities in a single entity with a standard framework.

The standard framework (Driver, Monitor and Sequencer) has evolved over a decade as part of the methodology developments and enhancements.

We can argue that feature segregation between VIP components depends upon protocols/standards. However there are common aspects which one need to be aware of and are important for controlling the flow of information within and outside the VIP.

This paper presentation highlights some of those techniques focused on ACTIVE path (Interactions between driver and sequence item) of the Verification IP.

Link: Abstarction_Levels.pdf

Abstract: Today’s traditional verification flow involves verification at multiple levels of abstraction. So the testbench also needs to be adjusted/modified at different abstractions from transaction-level simulation, RTL simulation to hardware acceleration.

An ideal solution is to make use of an advanced, automated verification environment across different abstraction levels, which helps in enhancing the overall performance gain, productivity and faster verification closure.

Thanks for reading, please inbox me for any queries/suggestions